# Lab Manual

for

# **Digital Computer Principles**

**Diploma In Computer Engineering**

3<sup>rd</sup> Semester

by

# SITTTR

## Kalamassery

#### STATE INSTITUTE OF TECHNICAL TEACHERS TRAINING AND RESEARCH

#### **GENERAL INSTRUCTIONS**

Rough record and Fair record are needed to record the experiments conducted in the laboratory. Rough records are needed to be certified immediately on completion of the experiment. Fair records are due at the beginning of the next lab period. Fair records must be submitted as neat, legible, and complete.

INSTRUCTIONS TO STUDENTS FOR WRITING THE FAIR RECORD

In the fair record, the index page should be filled properly by writing the corresponding experiment number, experiment name, date on which it was done and the page number.

On the **right side** page of the record following has to be written:

- 1. **Title**: The title of the experiment should be written in the page in capital letters.

- 2. In the left top margin, experiment number and date should be written.

- 3. Aim: The purpose of the experiment should be written clearly.

4.**Apparatus/Tools/Equipments/Components used:** A list of the Apparatus/Tools /Equipments /Components used for doing the experiment should be entered.

5. **Principle**: Simple working of the circuit/experimental set up/algorithm should be written.

6. **Procedure:** steps for doing the experiment and recording the readings should be briefly described(flow chart/programs in the case of computer/processor related experiments)

7. **Results**: The results of the experiment must be summarized in writing and should be fulfilling the aim.

8. Inference : Inference from the results is to be mentioned.

On the **Left side** page of the record following has to be recorded:

- 1. Circuit/Program: Neatly drawn circuit diagrams/experimental set up.

- 2. Design: The design of the circuit/experimental set up for selecting the components

should be clearly shown if necessary.

3. Observations: i) Data should be clearly recorded using Tabular Columns.

ii) Unit of the observed data should be clearly mentioned

iii) Relevant calculations should be shown. If repetitive calculations are needed, only show a sample calculation and summarize the others in a table.

4. **Graphs :** Graphs can used to present data in a form that show the results obtained, as one or more of the parameters are varied. A graph has the advantage of presenting large

amounts of data in a concise visual form. Graph should be in a square format.

#### **GENERAL RULES FOR PERSONAL SAFETY**

1. Always wear tight shirt/lab coat , pants and shoes inside workshops.

2. REMOVE ALL METAL JEWELLERY since rings, wrist watches or bands, necklaces, etc. make excellent electrodes in the event of accidental contact with electric power sources.

- 3. DO NOT MAKE CIRCUIT CHANGES without turning off the power.

- 4. Make sure that equipment working on electrical power are grounded properly.

- 5. Avoid standing on metal surfaces or wet concrete. Keep your shoes dry.

- 6. Never handle electrical equipment with wet skin.

- 7. Hot soldering irons should be rested in its holder. Never leave a hot iron unattended.

8. Avoid use of loose clothing and hair near machines and avoid running around inside lab .

TO PROTECT EQUIPMENT AND MINIMIZE MAINTENANCE:

**DO**: 1. SET MULTIRANGE METERS to highest range before connecting to an unknown source.

2. INFORM YOUR INSTRUCTOR about faulty equipment so that it can be sent for repair.

**DO NOT**: 1. Do not MOVE EQUIPMENT around the room except under the supervision of an instructor.

#### Index

#### **Cycle I - Implementation of basic logic gates**

1. Gates using basic components

| 2.  | Gates using IC                                                 | 6          |  |  |  |  |  |  |

|-----|----------------------------------------------------------------|------------|--|--|--|--|--|--|

| 3.  | Demonstration of Universal Gates                               | 9          |  |  |  |  |  |  |

| 4.  | SOP and POS                                                    | 11         |  |  |  |  |  |  |

|     | <b>Cycle II - Combinational Circuits</b>                       |            |  |  |  |  |  |  |

| 5.  | Parity bit generator                                           | 14         |  |  |  |  |  |  |

| 6.  | Code converters                                                | 16         |  |  |  |  |  |  |

| 7.  | Half-adder & a full-adder                                      | 22         |  |  |  |  |  |  |

| 8.  | Binary parallel adder, Adder- Subtractor, and a Magnitude Comp | oarator-25 |  |  |  |  |  |  |

|     | Cycle III - Synchronous sequential logic                       |            |  |  |  |  |  |  |

| 9.  | Flip Flops                                                     | 28         |  |  |  |  |  |  |

| 10. | Up-Down counter with Enable                                    | 33         |  |  |  |  |  |  |

| 11. | Counter (User controlled counting pattern)                     | 37         |  |  |  |  |  |  |

| 12. | Ripple Counter, Synchronous counter and Decimal Counter        | 41         |  |  |  |  |  |  |

| 13. | Binary counter with Parallel Load                              | 45         |  |  |  |  |  |  |

| 14. | Shift Registers                                                | 47         |  |  |  |  |  |  |

## DIGITAL COMPUTER PRINCIPLES LAB

Lab Manual

## The Breadboard

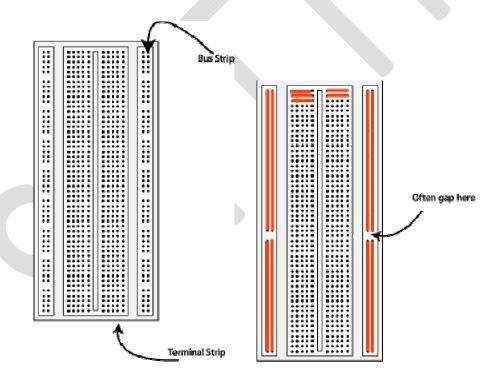

The breadboard consists of two terminal strips and two bus strips (often broken in the centre). Each bus strip has two rows of contacts. Each of the two rows of contacts is a node. That is, each contact along a row on a bus strip is connected together (inside the breadboard). Bus strips are used primarily for power supply connections, but are also used for any node requiring a large number of connections. Each terminal strip has 60 rows and 5 columns of contacts on each side of the centre gap. Each row of 5 contacts is a node.

You will build your circuits on the terminal strips by inserting the leads of circuit components into the contact receptacles and making connections with 22-26 gauge wire. There are wire cutter/strippers and a spool of wire in the lab. It is a good practice to wire +5V and 0V power supply connections to separate bus strips.

Fig. The breadboard. The lines indicate connected holes.

The 5V supply **MUST NOT BE EXCEEDED** since this will damage the ICs (Integrated circuits) used during the experiments. Incorrect connection of power to the ICs could result in them exploding or becoming very hot - with the **possible** serious injury occurring to the people working on the experiment! Ensure that

the power supply polarity and all components and connections are correct <u>before</u> switching on power.

#### **Building the Circuit**

Throughout these experiments we will use TTL chips to build circuits. The steps for wiring a circuit should be completed in the order described below:

- 1. Turn the power (Trainer Kit) off before you build anything!

- 2. Make sure the power is off before you build anything!

- 3. Connect the +5V and ground (GND) leads of the power supply to the power and ground bus strips on your breadboard.

- 4. Plug the chips you will be using into the breadboard. Point all the chips in the same direction with pin 1 at the upper-left corner. (Pin 1 is often identified by a dot or a notch next to it on the chip package)

- 5. Connect +5V and GND pins of each chip to the power and ground bus strips on the breadboard.

- 6. Select a connection on your schematic and place a piece of hook-up wire between corresponding pins of the chips on your breadboard. It is better to make the short connections before the longer ones. Mark each connection on your schematic as you go, so as not to try to make the same connection again at a later stage.

- 7. Get one of your group members to check the connections, **before** you turn the power on.

- 8. If an error is made and is not spotted before you turn the power on. Turn the power off immediately before you begin to rewire the circuit.

- 9. At the end of the laboratory session, collect you hook-up wires, chips and all equipment and return them to the demonstrator.

- 10. Tidy the area that you were working in and leave it in the same condition as it was before you started.

# Cycle I

## **Implementation of basic logic gates**

Exp.No...1...... Name of the Experiment: Gates using basic components

Aim: Implement logic gates using basic components

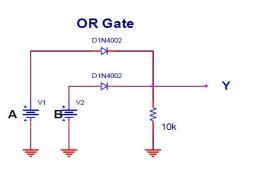

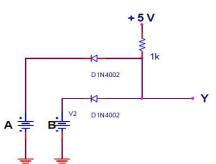

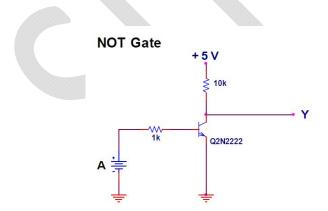

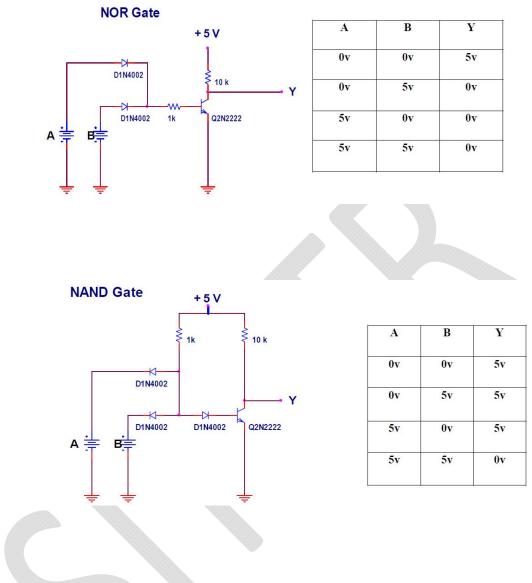

*Objectives:* To study the construction of logic gates (**OR**, **AND**, **NOT**, **NOR**, **NAND** gates etc.) using discrete components and verify their truth tables

*Components:* Bread board/ Kit, Resistors 10k,1k,220ohms, Transistors 2N2222(NPN), Diodes 1N 4001, Connecting wires

#### Theory:

- *a)* An OR gate is a logic circuit with two or more inputs and one output. The output of an OR gate is LOW only when all of its inputs are LOW. For all other possible input combinations, the output is HIGH

- b) The output of an AND gate is HIGH only when all of its inputs are in the HIGH state. In all other cases, the output is LOW

- c) A NOT gate is a one-input, one-output logic circuit whose output is always the complement of the input. That is, a LOW input produces a HIGH output, and vice versa.

- d) The output of a NOR gate is a logic '1' when all its inputs are logic '0'. For all other input combinations, the output is a logic '0'.

- e) The output of a NAND gate is a logic '0' when all its inputs are a logic '1'. For all other input combinations, the output is a logic '1'.

## Circuit diagrams

#### Circuit Diagrams:

# A B Y 0v 0v 0v 0v 5v 5v 5v 0v 5v 5v 5v 5v

TRUTH TABLE

| A  | В          | Y  |

|----|------------|----|

| 0v | <b>0</b> v | 0v |

| 0v | 5v         | 0v |

| 5v | <b>0</b> v | 0v |

| 5v | 5v         | 5v |

| Α  | Y  |

|----|----|

| 0v | 5v |

| 5v | 0v |

#### Procedure

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

- 3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

*Result*: Different logic gates are constructed and their truth tables are verified.

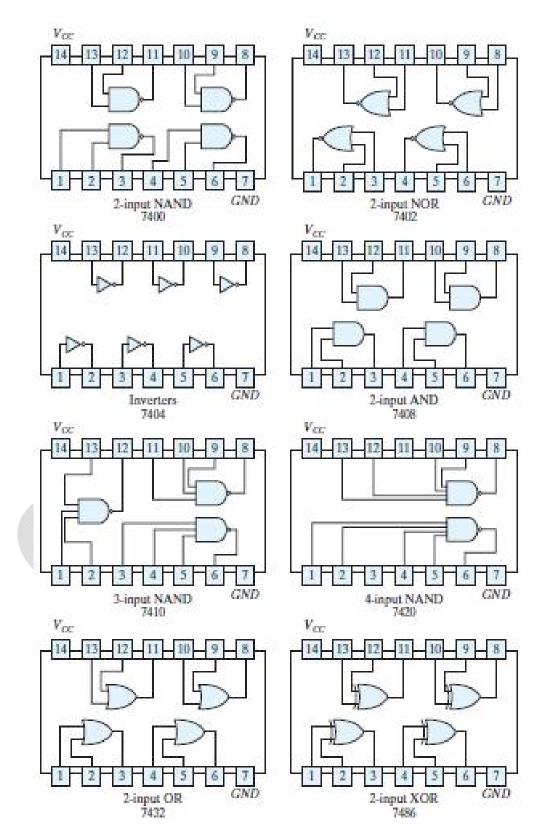

*Exp.No...2..... Name of the Experiment:* Gates using IC

*Aim:* Verify the Logic behavior of various IC gates: 7408, 7432, 7404, 7400, 7402, 7486

*Objectives:* To study the working of logic gates (**OR**, **AND**, **NOT**, **NOR**, **NAND**, **XOR** gates etc.) using IC and verify their truth tables *Components:* Bread board/ Kit , 7408, 7432, 7404, 7400, 7402, 7486

#### Theory:

- *a)* An OR gate is a logic circuit with two or more inputs and one output. The output of an OR gate is LOW only when all of its inputs are LOW. For all other possible input combinations, the output is HIGH

- b) The output of an AND gate is HIGH only when all of its inputs are in the HIGH state. In all other cases, the output is LOW

- c) A NOT gate is a one-input, one-output logic circuit whose output is always the complement of the input. That is, a LOW input produces a HIGH output, and vice versa.

- d) The output of a NOR gate is a logic '1' when all its inputs are logic '0'. For all other input combinations, the output is a logic '0'.

- e) The output of a NAND gate is a logic '0' when all its inputs are a logic

'1'. For all other input combinations, the output is a logic '1'. *Circuit and Truth table*

| Name     | Graphic<br>symbol | Algebraic<br>function             | Truth<br>table    |                       |  |  |

|----------|-------------------|-----------------------------------|-------------------|-----------------------|--|--|

|          | 19                |                                   | x y               | F                     |  |  |

| AND      | x                 | $F = \mathbf{x} \cdot \mathbf{y}$ | 0 1               | 0<br>0<br>0<br>1      |  |  |

| OR       | ;=)               | F F = x + y                       | 0 1               | F<br>0<br>1<br>1<br>1 |  |  |

| Inverter | x>•               | F = x'                            | x F<br>0 1<br>1 0 |                       |  |  |

|              |                 |                   | x   | У | F                   |

|--------------|-----------------|-------------------|-----|---|---------------------|

| NAND         | x - De-F        | F = (xy)'         | 0   | 0 | 1                   |

| NAND         | y / _ /         | $1 - (\lambda y)$ | 0   | 1 | 1                   |

|              |                 |                   | 1.5 | 0 | 1                   |

|              |                 |                   | 1   | 1 | 0                   |

|              |                 |                   | x   | y | F                   |

| NOR          | x<br>y<br>F     | F = (x + y)'      | 0   | 0 | 1                   |

| 190.00       |                 |                   | 0   | 1 | 0                   |

|              |                 |                   | 1   | 0 | 0                   |

|              |                 |                   | 1   | 1 | 0                   |

| Exclusive-OR | - Article - Art |                   | x   | Ţ | P                   |

|              |                 | F = xy' + x'y     | 0   | 0 | 0                   |

| (XOR)        |                 | = x ⊕ y           | 0   | 1 | $\langle 1 \rangle$ |

| 고민 것 -       | - 11-           | 8.58              | 1   | 0 | 1                   |

|              |                 |                   | 1   | 1 | - 0                 |

## Procedure

- a. Test all the ICs manually/ using IC tester.

- b. Connect VCC and the ground.

- c. Connect the appropriate pins to the input and output LEDs and switches.

- d. Verify the truth table with respect to the clock.

*Result* : Different logic gates and their truth tables are verified.

## **Useful IC Pin details**

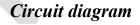

*Exp.No...3..... Name of the Experiment:* Demonstration of universal gates

Aim: Implement basic gates using Universal Gates (NAND & NOR)

*Objectives:* To study the design and implementation of logic gates (**OR**, **AND**, **NOT**, **NOR**, **NAND**, **XOR** gates etc.) using Universal Gates (NAND & NOR) and verify their truth tables

*Components:* Bread board/ Kit, 7400, 7402

#### Theory:

- *a*) An OR gate is a logic circuit with two or more inputs and one output. The output of an OR gate is LOW only when all of its inputs are LOW. For all other possible input combinations, the output is HIGH

- b) The output of an AND gate is HIGH only when all of its inputs are in the HIGH state. In all other cases, the output is LOW

- c) A NOT gate is a one-input, one-output logic circuit whose output is always the complement of the input. That is, a LOW input produces a HIGH output, and vice versa.

- d) The output of a NOR gate is a logic '1' when all its inputs are logic '0'. For all other input combinations, the output is a logic '0'.

- e) The output of a NAND gate is a logic '0' when all its inputs are a logic '1'. For all other input combinations, the output is a logic '1'.

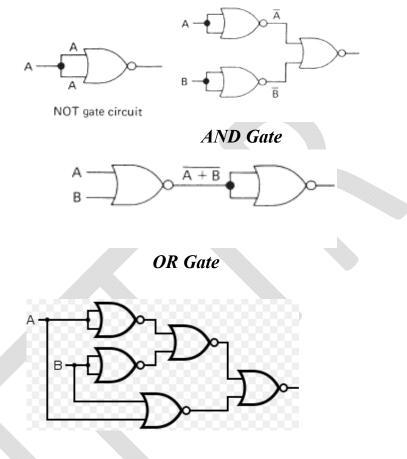

## **REALIZATION OF GATES USING NAND**

## **REALIZATION OF GATES USING NOR**

XOR Gate

Procedure

- a. Test all the ICs manually/ using IC tester.

- b. Connect VCC and the ground.

- c. Connect the appropriate pins to the input and output LEDs and switches.

- d. Verify the truth table with respect to the clock.

*Result* Different logic gates are constructed and their truth tables are verified.

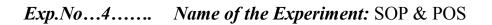

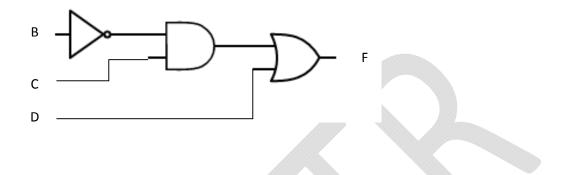

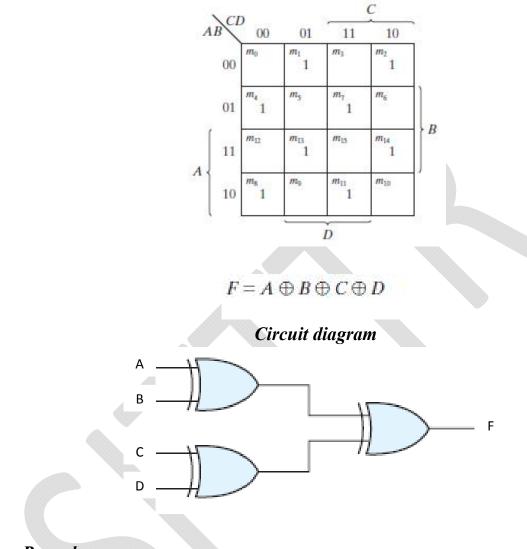

*Aim:* Plot the following Boolean function in a Map as well as implement in a logic diagram

F = A'D + BD + B'C + AB'D

**Objectives:** To Study the Simplification of Boolean Functions SOP & POS forms (Demonstrates the relationship between a Boolean Function and the corresponding logic diagram – using Map reduction method)

Components: Bread board/ Kit, 7408,7404,7432

#### Theory:

- *a*) Convert the given function in Standard SOP Form., Enter into K-Map and reduce it.

- b) Convert the given function in Standard POS Form., Enter into K-Map and reduce it.

- c) Verify that (a) and (b) is equal

#### Convert the given function in to Standard SOP Form

F = A'D + BD + B'C + AB'D

Since it is in SOP convert to Std SOP

- \*) Add the variable B for the missing terms A'D=A'D(B+B')=A'DB+A'DB'

- \*) Add the variable A for the missing terms BD=BD(A'+A)=A'BD+ABD

- B'C=B'C(A'+A)=A'B'C+AB'C

- \*) Add the variable C for the missing terms

- A'DB=A'DB(C'+C)=A'DBC'+A'DBC

- A'DB'=ADB'(C'+C)=ADB'C'+ADB'C

- A'BD=A'BD(C'+C)=A'BDC'+A'BDC

- ABD=ABD(C'+C)=ABDC'+ABDC

- AB'D=AB'D(C'+C)=AB'DC'+AB'DC

- \*) Add the variable D for the missing terms A'B'C=A'B'C(D'+D)= A'B'CD'+ A'B'CD

- AB'C=AB'C(D'+D)=AB'CD'+AB'CD

- \*) combine the above four variable terms all together

- F=A'BC'D+A'BCD+A'B'C'D+A'B'CD+A'BC'D+A'BCD+ABC'D

- +ABCD+AB'C'D+AB'CD+A'B'CD'+ A'B'CD +AB'CD' +AB'CD

- Ie F= m(1,2,3,5,7,9,10,11,13,15)

- Ie f= M(0,4,6,8,12,14)

### Enter into K-map and minimise

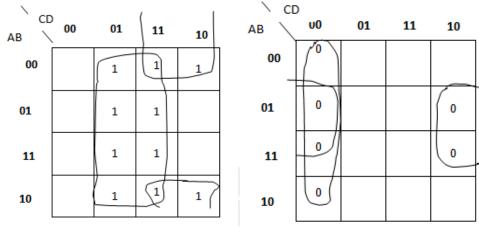

Sop F min=D+B'C

POS F max=(C+D)(B'+D)

Truth table for Sop F min=D+B'C

| fram aore for bop I min |   |   |     |       |  |  |  |  |

|-------------------------|---|---|-----|-------|--|--|--|--|

| C                       | В | D | B'C | D+B'C |  |  |  |  |

| 0                       | 0 | 0 | 0   | 0     |  |  |  |  |

| 0                       | 0 | 1 | 0   | 1     |  |  |  |  |

| 0                       | 1 | 0 | 0   | 0     |  |  |  |  |

| 0                       | 1 | 1 | 0   | 1     |  |  |  |  |

| 1                       | 0 | 0 | 1   | 1     |  |  |  |  |

| 1                       | 0 | 1 | 1   | 1     |  |  |  |  |

| 1                       | 1 | 0 | 0   | 0     |  |  |  |  |

| 1                       | 1 | 1 | 0   | 1     |  |  |  |  |

|                         |   |   |     |       |  |  |  |  |

POS F max=(C+D)(B'+D)

| С | В | D | C+D | B'+D | (C+D)(B'+D) |

|---|---|---|-----|------|-------------|

| 0 | 0 | 0 | 0   | 1    | 0           |

| 0 | 0 | 1 | 1   | 1    | 1           |

| 0 | 1 | 0 | 0   | 0    | 0           |

| 0 | 1 | 1 | 1   | 1    | 1           |

| 1 | 0 | 0 | 1   | 1    | 1           |

| 1 | 0 | 1 | 1   | 1    | 1           |

| 1 | 1 | 0 | 1   | 0    | 0           |

| 1 | 1 | 1 | 1   | 1    | 1           |

The above Truth table shows both are equal but in SOP minimized equation needs 3 gate and POS minimized equation needs 4 gates; so here SOP minimized equation is more economical

#### Procedure

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

- 3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

*Result* : Different logic circuit are constructed and their truth tables are verified.

## Cycle 2

## **Combinational Circuits**

*Exp.No...5...... Name of the Experiment:* Parity bit generator *Aim:* Design, construct, and test circuit that generates parity bit from four message bits

**Objectives:** To study the construction and design of the Combinational Circuits

#### Components: Bread board/ Kit, 7486

**Theory:** A parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message, including the parity bit, is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a *parity generator*

#### Circuit diagram and truth table

#### Truth table

| A | B | С | D | P |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

#### Procedure

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

*Result* : Different logic circuit are constructed and their truth tables are verified.

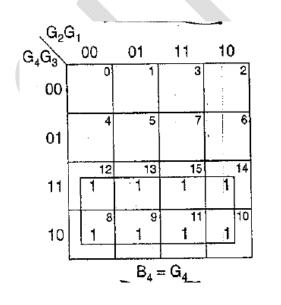

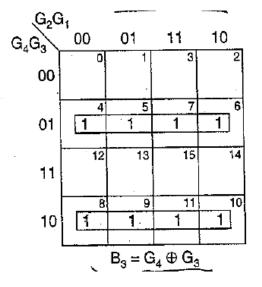

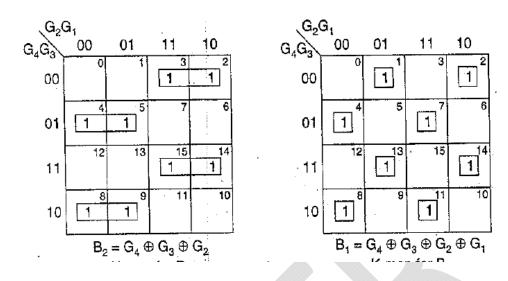

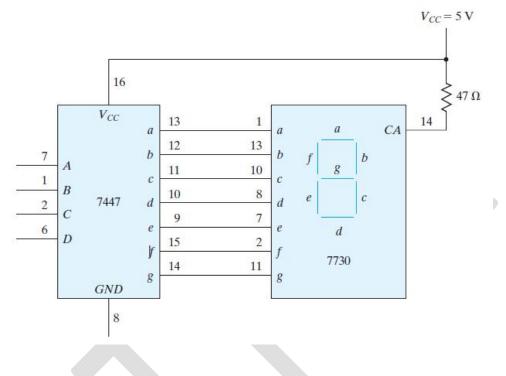

*Exp.No...6...... Name of the Experiment:* Code converter*Aim:* Design a circuit that converts a 1) Gray code to binary, 2) Decoder for a binary digit to BCD, and 3) a seven segment indicator*Objectives:* To study the design, implementation and the working of code converters.

Components: Bread board/ Kit, 7486,7408, 7432, 7404, 7730, 7447

Theory:

#### Gray code to binary,

- a) Most significant bit (B<sub>1</sub>) is same as the most significant bit in Gray Code (B<sub>1</sub> = G<sub>1</sub>)

- b) To find next bit perform Ex-OR (Exclusive OR) between the Current binary bit and previous bit.

C = P. (Fr. OP) P.

$G_n = B_n (Ex-OR) B_{n-1}$

## **Binary digit to BCD**

A binary code that distinguishes among 10 elements must contain at least four bits, but 6 out of the 16 possible combinations remain unassigned. Different binary codes can be obtained by arranging four bits into 10 distinct combinations.

A decimal number in BCD is the same as its equivalent binary number only when the number is between 0 and 9. A BCD number greater than 10 looks different from its equivalent binary number, even though both contain 1's and 0's. Moreover, the binary combinations 1010 through 1111 are not used and have no meaning in BCD

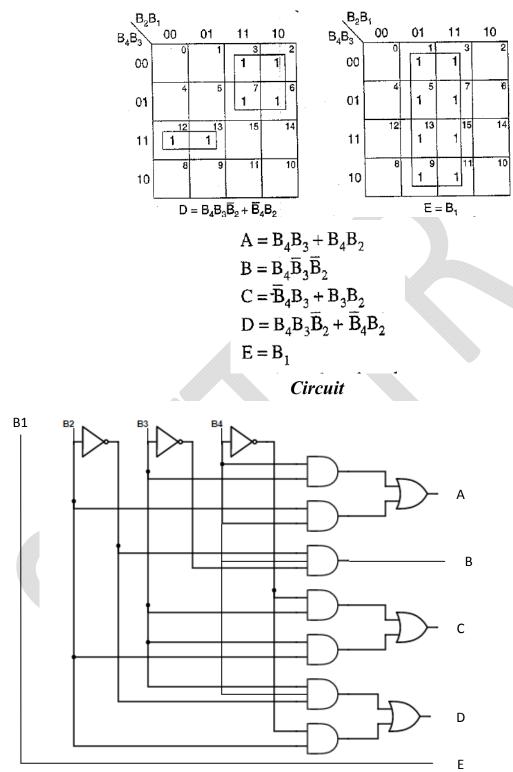

#### Seven segment indicator

A seven-segment indicator is used to display any one of the decimal digits 0 through 9. Usually, the decimal digit is available in BCD. A BCD-to-seven-segment decoder accepts a decimal digit in BCD and generates the corresponding seven-segment code

#### Circuit and truth table

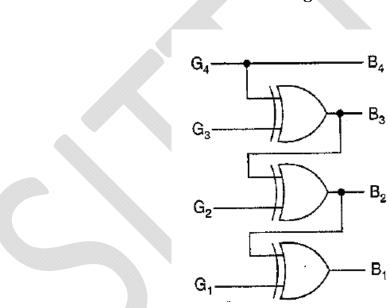

## Gray code to binary

#### Truth table

|       | 4-bit (        | Gray           |     | 4-bit binary   |                |                |                |

|-------|----------------|----------------|-----|----------------|----------------|----------------|----------------|

| $G_4$ | G <sub>3</sub> | G <sub>2</sub> | G,  | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | Β <sub>1</sub> |

| 0     | 0              | 0              | 0   | 0              | 0              | 0              | 0              |

| 0     | 0              | 0              | 1   | . 0            | 0              | 0              | 1              |

| 0     | 0              | 1              | t   | 0              | 0              | 1              | 0              |

| 0     | 0              | 1              | 0   | 0              | 0              | <u></u> 1      | 1              |

| 0     | 1              | 1              | 0   | 0              | 1              | 0              | 0              |

| 0     | 1              | 1              | 1   | 0              | 1              | 0              | 1              |

| 0     | 1              | 0              | 1   | 0              | 1              | 1              | 0              |

| 0     | 1              | 0              | 0   | 0              | 1              | 1              | 1              |

| 1     | 1              | 0              | 0   | 1              | 0              | 0              | 0              |

| 1     | 1              | 0              | 1   | 1              | 0              | 0              | 1              |

| 1     | 1              | 1              | 1   | 1              | 0              | 1              | 0              |

| 1     | Ť              | 1              | 0   | 1              | 0              | · 1            | 1              |

| 1     | 0              | 1              | 0   | 1              | 1              | 0              | 0              |

| 1     | 0              | 1              | 1   | 1              | 1              | 0              | 1              |

| 1     | 0              | 0              | 1   | 1              | 1              | 1              | 0              |

| 1     | 0              | 0              | . 0 | 1              | 1              | 1              | 1              |

K-map

Circuit diagram

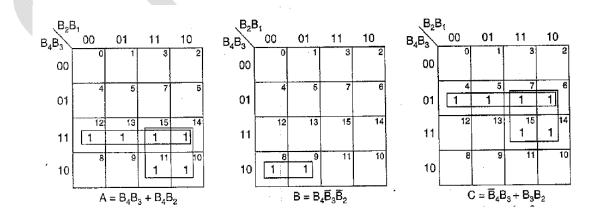

## 4 bit Binary to BCD Converter Truth Table

|         | 4-bit binary   |       |                | BCD output     |  |     |   |   |   |    |

|---------|----------------|-------|----------------|----------------|--|-----|---|---|---|----|

| Decimal | B <sub>4</sub> | $B_3$ | B <sub>2</sub> | B <sub>1</sub> |  | A   | B | С | D | Ε  |

| 0       | 0              | 0     | 0              | 0              |  | 0   | 0 | 0 | 0 | 0  |

| 1       | 0              | 0     | 0              | 1              |  | 0   | 0 | 0 | 0 | 1  |

| 2       | 0              | 0     | 1              | 0              |  | 0   | 0 | 0 | 1 | 0  |

| 3       | 0              | 0     | 1              | 1              |  | 0   | 0 | 0 | 1 | 1  |

| 4       | 0              | 1     | 0              | 0              |  | 0   | 0 | 1 | 0 | .0 |

| 5       | 0              | 1     | 0              | 1              |  | 0   | 0 | 1 | 0 | ·1 |

| 6       | 0              | 1     | 1              | 0              |  | 0   | 0 | 1 | 1 | 0  |

| 7       | 0              | 1     | 1              | 1              |  | 0   | 0 | 1 | 1 | 1  |

| 8 .     | 1              | 0     | 0              | 0              |  | 0   | 1 | 0 | 0 | .0 |

| 9       | 1              | 0     | 0              | 1              |  | 0   | 1 | 0 | 0 | 1  |

| 10      | 1              | 0     | 1              | 0              |  | 1   | 0 | õ | 0 | 0  |

| -11     | · 1            | 0     | 1              | 1              |  | 1   | 0 | 0 | 0 | 1  |

| .12     | <u> </u>       | 1     | 0              | 0              |  | - 1 | 0 | 0 | 1 | 0  |

| 13      | 1              | 1     | 0              | -1             |  | 1   | 0 | 0 | 1 | 1  |

| 14      | 1              | 1     | 1              | 0              |  | 1   | 0 | 1 | 0 | 0  |

| 15      | 1              | 1     | 1              | 1              |  | 1   | 0 | 1 | 0 | 1  |

$A = \Sigma m(10, 11, 12, 13, 14, 15)$   $B = \Sigma m(8, 9)$   $C = \Sigma m(4, 5, 6, 7, 14, 15)$   $D = \Sigma m(2, 3, 6, 7, 12, 13)$  $E = \Sigma m(1, 3, 5, 7, 9, 11, 13, 15)$

#### Seven segment indicator

Construct the circuit shown in Fig. . Apply the four-bit BCD digits through four switches, and observe the decimal display from 0 to 9. Inputs 1010 through

Diploma

1111 have no meaning in BCD. Depending on the decoder, these values may cause either a blank or a meaningless pattern to be displayed. Observe and record the output patterns of the six unused input combinations.

#### Procedure

1. Connections are made as per the circuit diagram

2. Switch on the power supply

3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

*Result* : Different logic circuit are constructed and their truth tables are verified.

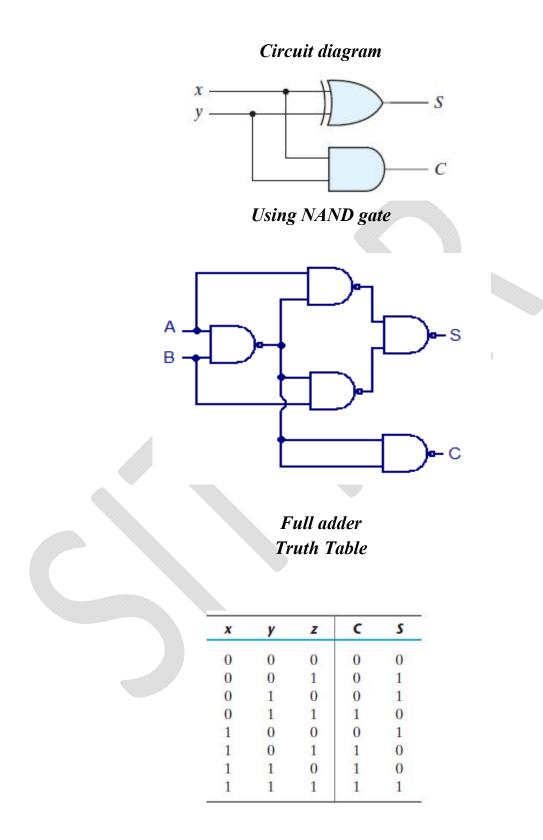

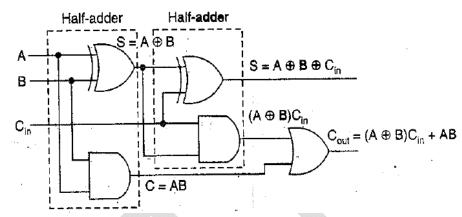

*Exp.No...7..... Name of the Experiment:* Half-adder & Full-adder *Aim:* Design, construct, and test a half-adder & a full-adder *Objectives:* To study the Design, construction, and the working of adders using desecrate Gates *Components:* Bread board/ Kit, 7486, 7408, 7400 & 7432 *Theory:*

**Half adder**: circuit needs two binary inputs and two binary outputs. The input variables designate the augend and addend bits; the output variables produce the sum and carry. We assign symbols x and y to the two inputs and S (for sum) and C (for carry) to the outputs. The truth table for the half adder is listed in Table **Full adder :** A full adder is a combinational circuit that forms the arithmetic sum of three bits. It consists of three inputs and two outputs. Two of the input variables, denoted by x and y, represent the two significant bits to be added. The third input, z, represents the carry from the previous lower significant position.

Circuit and truth table

|   | alf Ado<br>ruth tai |   |   |

|---|---------------------|---|---|

| x | y                   | c | S |

| 0 | 0                   | 0 | 0 |

| 0 | 1                   | 0 | 1 |

| 1 | 0                   | 0 | 1 |

| 1 | 1                   | 1 | 0 |

The simplified Boolean functions for the two outputs can be obtained directly from the truth table.

$$S = x'y + xy'$$

$$C = xy$$

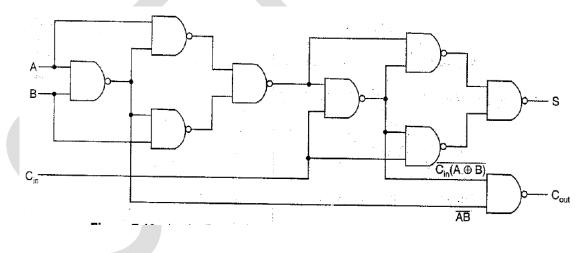

$$\int S = \overline{A}\overline{B}C_{in} + \overline{A}B\overline{C}_{in} + A\overline{B}\overline{C}_{in} + ABC_{in}$$

$$= (A\overline{B} + \overline{A}B)\overline{C}_{in} + (AB + \overline{A}\overline{B})C_{in} = (A \oplus B)\overline{C}_{in} + (\overline{A \oplus B})C_{in} = A \oplus B \oplus C_{in}$$

$$C_{out} = \overline{A}BC_{in} + A\overline{B}C_{in} + AB\overline{C}_{in} + ABC_{in} = AB + (A \oplus B)C_{in} = AB + AC_{in} + BC_{in}$$

Circuit

Circuit using NAND gate

#### Procedure

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

*Result* : Different logic circuit are constructed and their truth tables are verified.

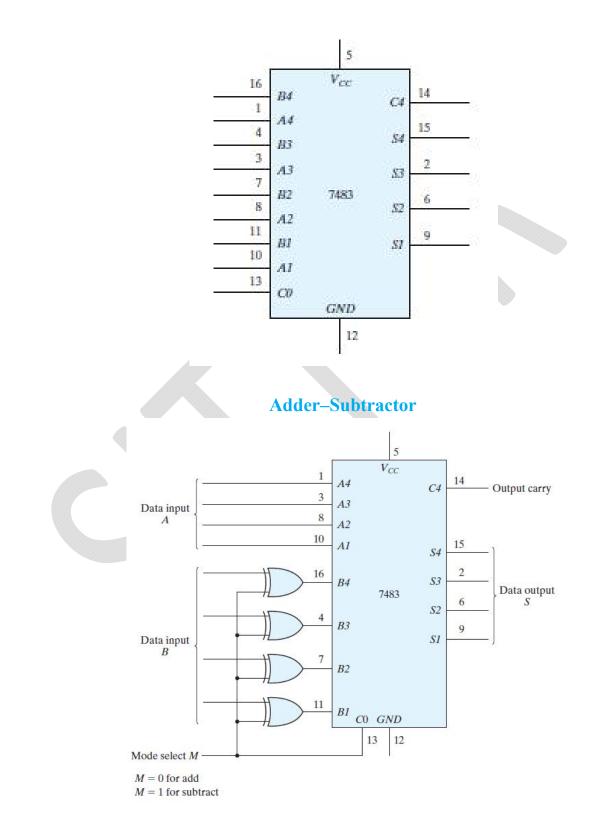

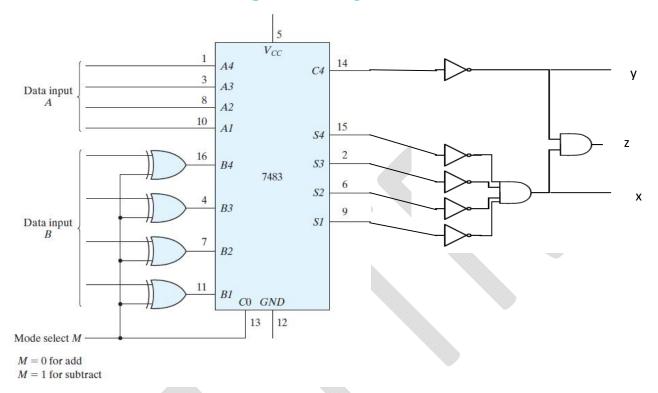

*Exp.No...8...... Name of the Experiment:* Binary parallel adder, Adder-Subtractor, and a Magnitude Comparator

Aim: Implement a circuit using a four-bit binary parallel adder (IC 7483) implement Adder- Subtractor, and a Magnitude Comparator

Objectives: To study the implementation of parallel adder, Adder- Subtractor, and a Magnitude Comparator using IC 7483

Components: Bread board/ Kit, 7404, 7408 & 7483

Theory:

Parallel adder : IC type 7483 is a four-bit binary parallel adder. The pin assignment is shown in Fig.. The 2 four-bit input binary numbers are A1 through A4 and B1 through B4. The four-bit sum is obtained from S1 through S4. C0 is the

input carry and C4 the output carry.

Adder–Subtractor: Two binary numbers can be subtracted by taking the 2's complement of the subtrahend and adding it to the minuend. The 2's complement can be obtained by taking the 1's complement and adding 1. To perform A - B, we complement the four bits of B, add them to the four bits of A, and add 1 through the input carry.

**Magnitude Comparator :** The comparison of two numbers is an operation that determines whether one number is greater than, equal to, or less than the other number. Two numbers, *A* and *B*, can be compared by first subtracting *A* - *B*. If the output in *S* is equal to zero, then A = B. The output carry from *C4* determines the relative magnitudes of the numbers: When C4 = 1,  $A \cup B$ ; when C4 = 0,  $A \in B$ ; and when C4 = 1 and  $S_0$ ,  $A \in T B$ . It is necessary to supplement the subtractor circuit of Fig. to provide the comparison logic. This is done with a combinational circuit that has five inputs—*S1* through *S4* and *C4* —and three outputs, designated by *x*, *y*, and *z*, so that

x = 1 if A = B (S = 0000)y = 1 if A < B (C4 = 0) z = 1 if A > B (C4 = 1 and S 0000)

The combinational circuit can be implemented with the 7404 and 7408 ICs. Construct the comparator circuit and test its operation. Use at least two sets of numbers for A and B to check each of the outputs x, y, and z.

## Circuit

## Parallel adder

#### **Magnitude Comparator**

#### Procedure

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

*Result* : Different logic circuit are constructed and their truth tables are verified.

## Cycle 3-

## Synchronous sequential logic

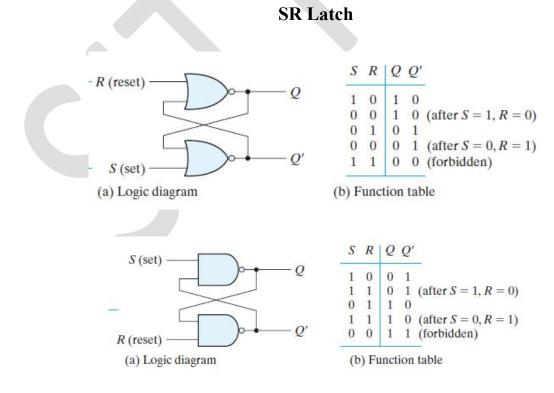

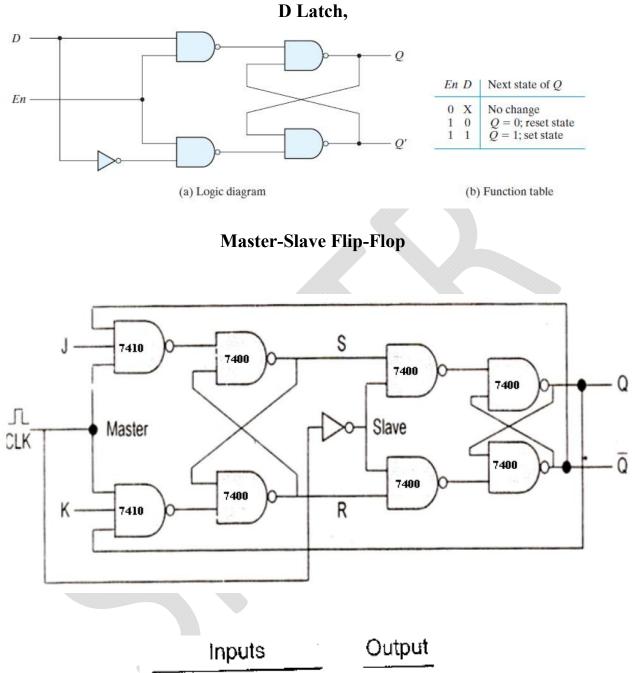

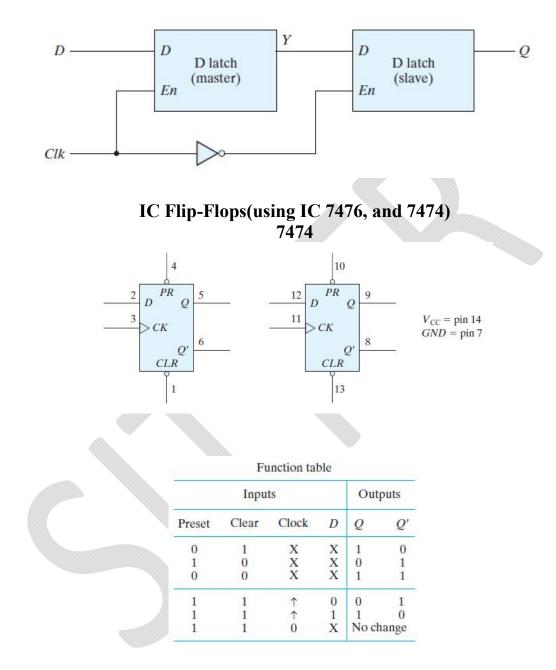

Exp.No...9...... Name of the Experiment: Flip-Flops

*Aim:* Construct, Test, and investigate the operation of SR Latch, D Latch, Master-Slave Flip-Flop, Edge-Triggered Flip-Flop, IC Flip-Flops(using IC 7476, and 7474)

*Objectives:* To study the Construction and the working of SR Latch, D Latch, Master-Slave Flip-Flop, Edge-Triggered Flip-Flop, IC Flip-Flops *Components:* Bread board/ Kit, 7476, 7474, 7400, 7402 & 7404 *Theory:*

**SR Latch**,: The *SR* latch is a circuit with two cross-coupled NOR gates or two cross-coupled NAND gates, and two inputs labeled *S* for set and *R* for reset. The *SR* latch constructed with two cross-coupled NOR gates is shown in Fig. . The latch has two useful states. When output Q = 1 and  $Q_{-} = 0$ , the latch is said to be in the *set state*. When Q = 0 and  $Q_{-} = 1$ , it is in the *reset state*. Outputs *Q* and *Q\_* are normally the complement of each other. However, when both inputs are equal to 1 at the same time, a condition in which both outputs are then switched to 0 simultaneously, the device will enter an unpredictable or undefined state or a metastable state.

**D** Latch : This latch has only two inputs: D (data) and En (enable). The D input goes directly to the S input, and its complement is applied to the R input. As long as the enable input is at 0, the cross-coupled SR latch has both inputs at the 1 level and the circuit cannot change state regardless of the value of D. The D input is sampled when En = 1. If D = 1, the Q output goes to 1, placing the circuit in the set state. If D = 0, output Q goes to 0, placing the circuit in the reset state. The D latch receives that designation from its ability to hold *data* in its internal storage.

**Master-Slave Flip-Flop,:** Observe that the master changes when the pulse goes positive and the slave follows the change when the pulse goes negative.

**Edge-Triggered Flip-Flop:** The construction of a D flip-flop with two D latches and an inverter is shown in Fig. The first latch is called the master and the second the slave. The circuit samples the D input and changes its

output Q only at the negative edge of the synchronizing or controlling clock (designated as Clk). When the clock is 0, the output of the inverter is 1. The slave latch is enabled, and its output Q is equal to the master output Y. The master latch is disabled because Clk = 0. When the input pulse changes to the logic-1 level, the data from the external D input are transferred to the master. The slave, however, is disabled as long as the clock remains at the 1 level, because its *enable* input is equal to 0. Any change in the input changes the master output at Y, but cannot affect the slave output. When the clock pulse returns to 0, the master is disabled and is isolated from the D input. At the same time, the slave is enabled and the value of Y is transferred to the output of the flip-flop at Q. Thus, a change in the output of the flip-flop can be triggered only by and during the transition of the clock from 1 to 0. C

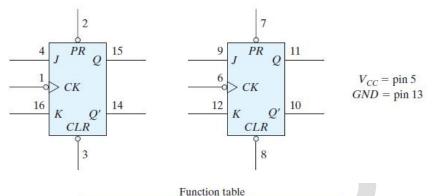

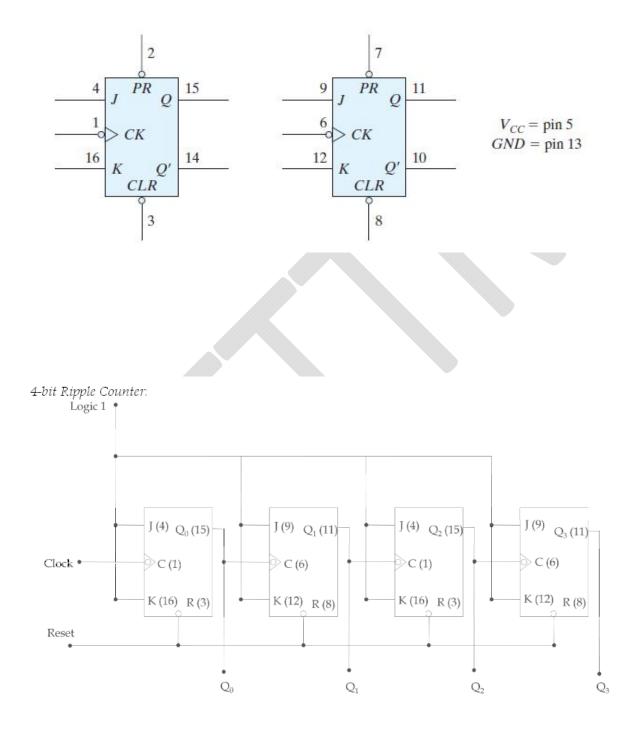

**Flip-Flops(using IC 7476, and 7474):** IC type 7476 consists of two JK master–slave flip-flops with preset and clear. The pin assignment for each flip-flop is shown in Fig IC type 7474 consists of two D positive-edge-triggered flip-flops with preset and clear. The pin assignment is shown in Fig.

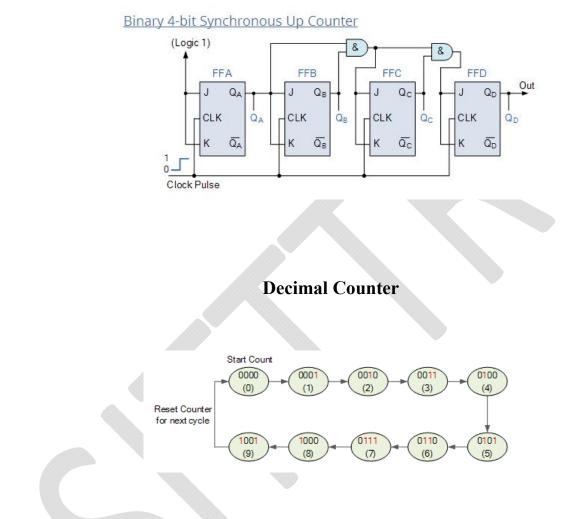

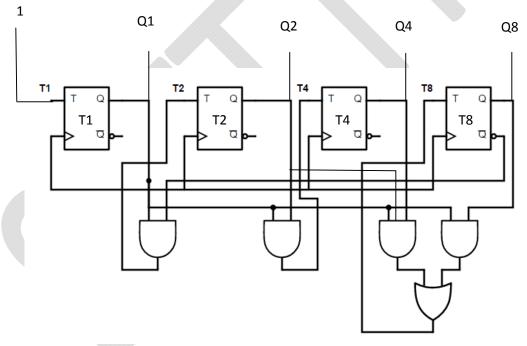

#### Circuit

|   | Input | 5      | Output             |  |

|---|-------|--------|--------------------|--|

| J | ĸ     | С      | Q                  |  |

| 0 | 0     |        | Q <sub>o</sub>     |  |

| 0 | 1     |        | ્ં                 |  |

| 1 | o     | $\Box$ | 1,                 |  |

| 1 | 1     |        | $\overline{Q}_{o}$ |  |

## **Edge-Triggered Flip-Flop**

|        | -     | Inputs |   |   | Out | tputs   |

|--------|-------|--------|---|---|-----|---------|

| Preset | Clear | Clock  | J | K | Q   | 1<br>Q' |

| 0      | 1     | х      | Х | Х | 1   | 0       |

| 1      | 0     | X      | X | X | 0   | 1       |

| 0      | 0     | X      | X | X | 1   | 1       |

| 1      | 1     |        | 0 | 0 | Noc | hange   |

| 1      | 1     |        | 0 | 1 | 0   | 1       |

| 1      | 1     |        | 1 | 0 | 1   | 0       |

| 1      | 1     |        | 1 | 1 | То  | ggle    |

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

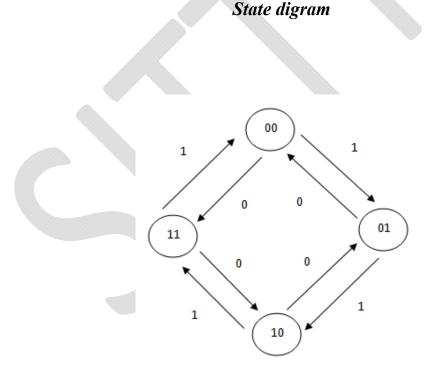

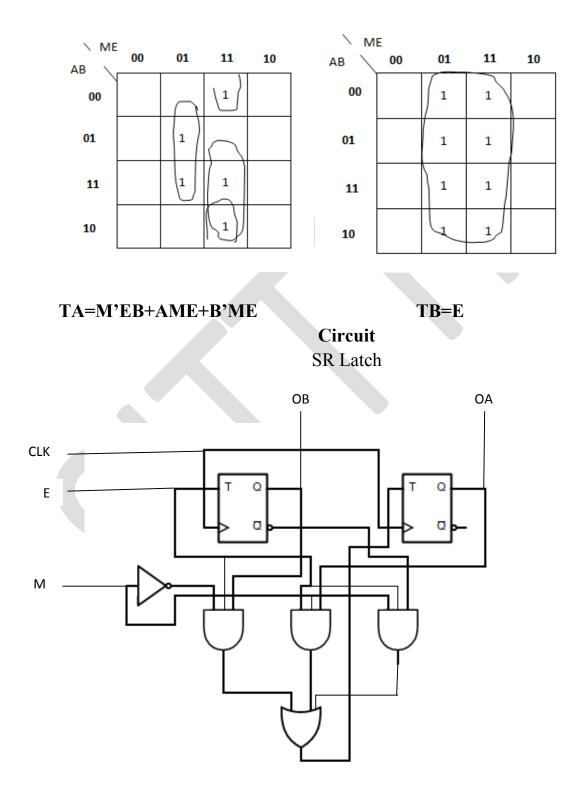

*Exp.No...10...... Name of the Experiment:* Up-Down counter with Enable Aim: Sequential Circuits (Design, construct, and test Up-Down counter with Enable)

**Objectives:** To study the design, implementation and the working of Sequential Circuits.

Components: Bread board/ Kit, 7410, 7404, NTE754, 744075 Theory:

Design, construct, and test a two-bit counter that counts up or down. An enable input E determines whether the counter is on or off. If E = 0, the counter is disabled and remains at its present count even though clock pulses are applied to the flip-flops. If E = 1, the counter is enabled and a second input, x, determines the direction of the count. If x = 1, the circuit counts upward with the sequence 00, 01, 10, 11, and the count repeats. If x = 0, the circuit counts downward with the sequence 11, 10, 01, 00, and the count repeats. Do not use E to disable the clock. Design the sequential circuit with *E* and *x* as inputs.

## Circuit

| PS             | NS                      | <b>Required</b> input |

|----------------|-------------------------|-----------------------|

| Q <sub>n</sub> | Q <sub><i>n</i>+1</sub> | T                     |

| 0              | 0                       | 0                     |

| 0              | 1                       | 1                     |

| 1              | 0                       | 1                     |

| 1              | 1                       | 0                     |

# T ff Excitation Table

| A | B | M | E | <b>O</b> A | OB | TA | TB |

|---|---|---|---|------------|----|----|----|

| 0 | 0 | 0 | 0 | 0          | 0  | 0  | 0  |

| 0 | 0 | 0 | 1 | 0          | 1  | 0  | 1  |

| 0 | 0 | 1 | 0 | 0          | 0  | 0  | 0  |

| 0 | 0 | 1 | 1 | 1          | 1  | 1  | 1  |

| 0 | 1 | 0 | 0 | 0          | 1  | 0  | 0  |

| 0 | 1 | 0 | 1 | 1          | 0  | 1  | 1  |

| 0 | 1 | 1 | 0 | 0          | 1  | 0  | 0  |

| 0 | 1 | 1 | 1 | 0          | 0  | 0  | 1  |

| 1 | 0 | 0 | 0 | 1          | 0  | 0  | 0  |

| 1 | 0 | 0 | 1 | 1          | 1  | 0  | 1  |

| 1 | 0 | 1 | 0 | 1          | 0  | 0  | 0  |

| 1 | 0 | 1 | 1 | 0          | 1  | 1  | 1  |

| 1 | 1 | 0 | 0 | 1          | 1  | 0  | 0  |

| 1 | 1 | 0 | 1 | 0          | 0  | 1  | 1  |

| 1 | 1 | 1 | 0 | 1          | 1  | 0  | 0  |

| 1 | 1 | 1 | 1 | 1          | 0  | 1  | 1  |

Note:- M=0= Up, M=1=Down, E=0=No Change, E=1=Change

# Truth table

- 1. Connections are made as per the circuit diagram

- 2. Switch on the power supply

- 3. Apply different combinations of inputs and observe the outputs; compare the outputs with the truth tables

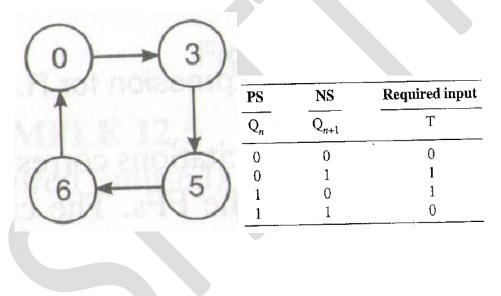

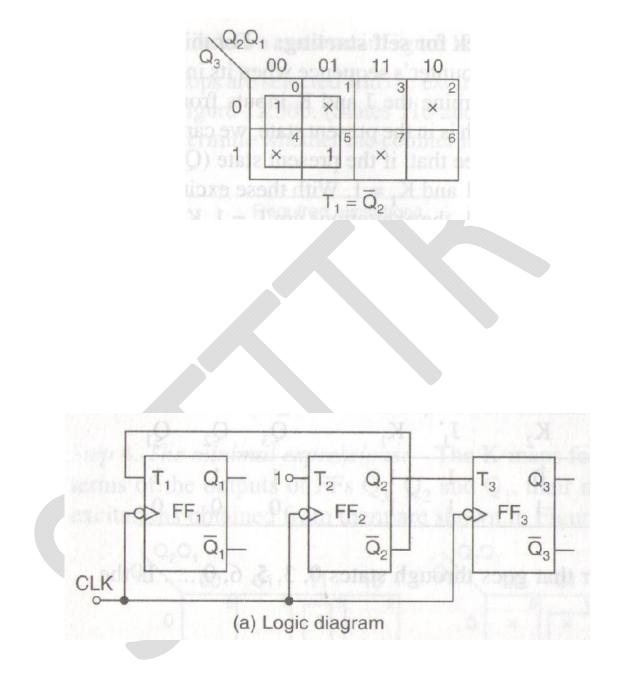

*Exp.No...11...... Name of the Experiment:* Counter (User controlled counting pattern)

*Aim:* Design, construct, and test a counter that goes through a sequence of binary states (User controlled counting pattern) : 0, 3,5,6, and back to 0 *Objectives:* To study the design, construction, and working of counter with User controlled counting pattern

Components: Bread board/ Kit, NTE754

## Theory:

Design, construct, and test a counter that goes through the following sequence of binary states: 0, 3,5,6, and back to 0 to repeat

# Circuit State digram

**Excitation** Table

|                                 |    | PS             |             |                | NS             |                       |                |                | And in case of the local division of the loc | tions          |  |  |

|---------------------------------|----|----------------|-------------|----------------|----------------|-----------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

|                                 |    | Q <sub>2</sub> | Q           | Q <sub>3</sub> | Q <sub>2</sub> | Q <sub>1</sub>        | T <sub>3</sub> | T              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | T <sub>1</sub> |  |  |

|                                 | 0  | 0              | 0           | 0              | 1              | 1 0                   | 0              | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1              |  |  |

|                                 | 0  | 1              | 1           | 1              | 0              | 1                     | 1              | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0              |  |  |

|                                 | 1  | 0              | 1           | 1              | 010            | 0                     | 0              | 0101           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100            |  |  |

|                                 | 1  | 1              | 0           | 0              | 0              | 0                     | Tool)          | 1              | 51.311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0              |  |  |

|                                 |    |                |             |                |                |                       |                | CSN CONTRACTOR |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|                                 |    |                |             |                |                |                       |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

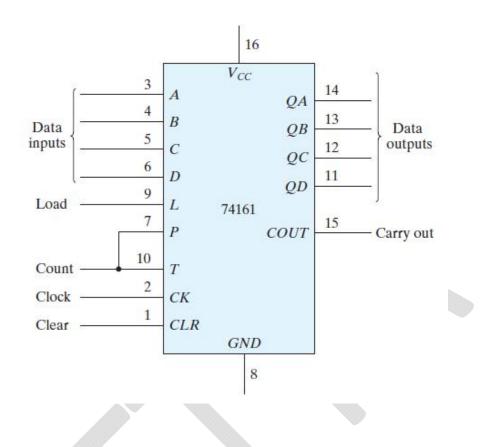

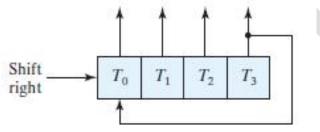

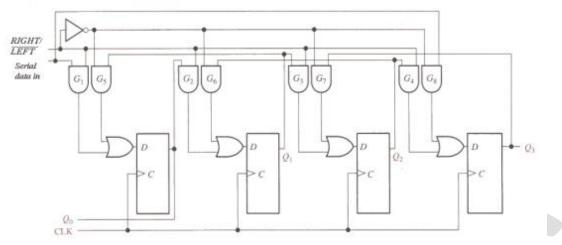

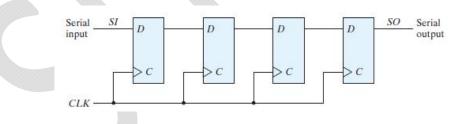

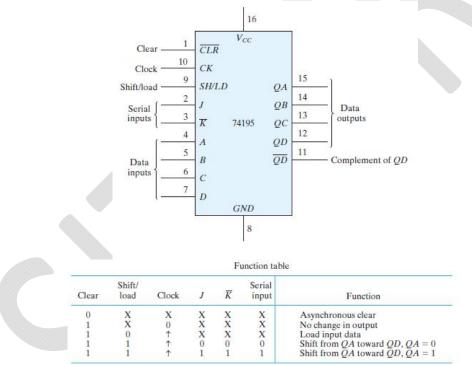

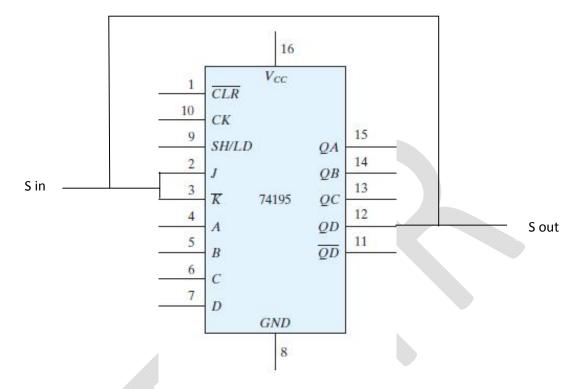

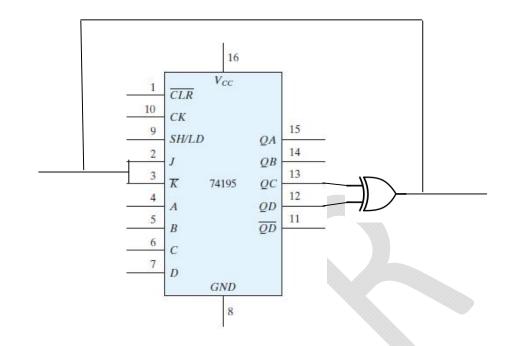

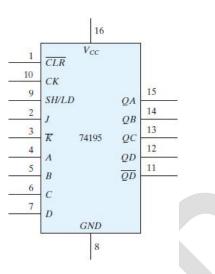

|                                 |    |                |             |                |                | . 0                   | 0              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |